La unitat de control és el component principal d'una unitat central de processament (CPU) en ordinadors que pot dirigir les operacions durant l'execució d'un programa mitjançant el processador / ordinador. La funció principal de la unitat de control és obtenir i executar instruccions de la memòria d’un ordinador. Rep la instrucció / informació d’entrada de l’usuari i la converteix en senyals de control , que després es lliuren a la CPU per a una posterior execució. S'inclou com a part de l'arquitectura Von Neumann desenvolupada per John Neumann. S’encarrega de proporcionar els senyals de temporització i de controlar els senyals i dirigeix l’execució d’un programa per part de la CPU. S'inclou com a part interna de la CPU en ordinadors moderns. En aquest article es descriu informació completa sobre la unitat de control.

Què és la unitat de control?

El component que rep el senyal / informació / instrucció d'entrada de l'usuari i es converteix en senyals de control per a l'execució a la CPU. Controla i dirigeix la memòria principal, la unitat aritmètica i lògica (ALU), els dispositius d’entrada i sortida, i també és responsable de les instruccions que s’envien a la CPU d’un ordinador. Obté les instruccions del fitxer memòria principal d'un processador i s'envia al registre d'instruccions del processador, que conté el contingut del registre.

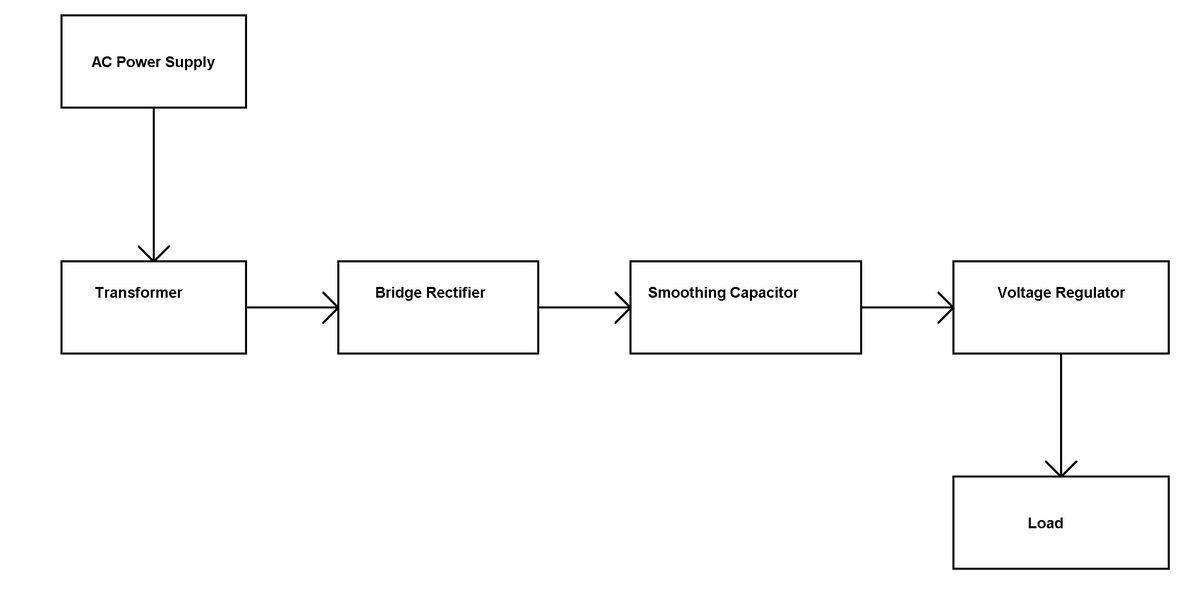

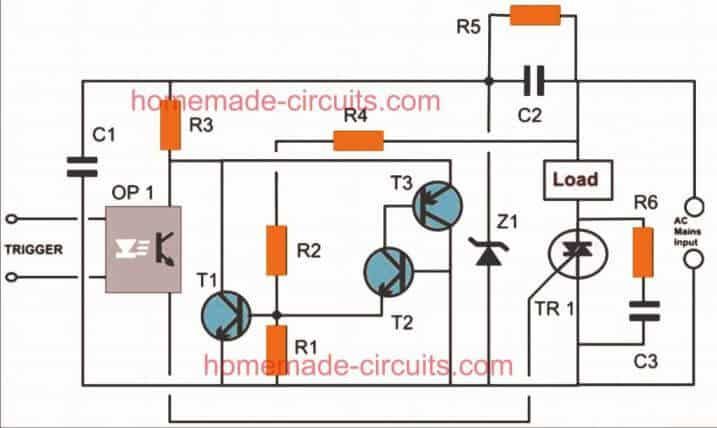

Diagrama de blocs de la unitat de control

La unitat de control converteix l'entrada en senyals de control i s'envia al processador i dirigeix l'execució d'un programa. Les operacions que s'han de realitzar són dirigides pel processador de l'ordinador. Principalment Unitat Central de Processament (CPU) i Unitat de Processament Gràfic (GPU) requereixen una unitat de control com a part interna. El diagrama de blocs de la unitat de control es mostra a la part superior.

Components d'una unitat de control

Els components d'aquesta unitat són instruccions registres , senyals de control dins de la CPU, senyals de control cap a / des del bus, bus de control, indicadors d'entrada i senyals de rellotge.

Els components de la unitat de control amb cable dur són registre d'instruccions (conté un camp d'opcode i adreça), unitat de temporització i estat de control generador , control de matriu de generació de senyals i descodificador d'instruccions.

Els components de la unitat de control micro programada són el següent generador d’adreces, un registre d’adreces de control, memòria de control i registre de dades de control.

Funcions

El funcions de la unitat de control inclou el següent.

- Dirigeix el flux de seqüència de dades entre el processador i altres dispositius.

- Pot interpretar les instruccions i controlar el flux de dades al processador.

- Genera la seqüència de senyals de control a partir de les instruccions rebudes o de les ordres del registre d’instruccions.

- Té la responsabilitat de controlar les unitats d’execució com ALU, memòries intermèdies de dades i registres a la CPU d’un ordinador.

- Té la possibilitat d'obtenir, descodificar, gestionar l'execució i emmagatzemar resultats.

- No pot processar i emmagatzemar les dades

- Per transferir les dades, es comunica amb els dispositius d’entrada i sortida i controla totes les unitats de l’ordinador.

Disseny de la Unitat de Control

El disseny d'això es pot fer utilitzant dos tipus d’una unitat de control que inclouen els següents.

- Basat en cable dur

- Basat en microprogramació (d'un sol nivell i de dos nivells)

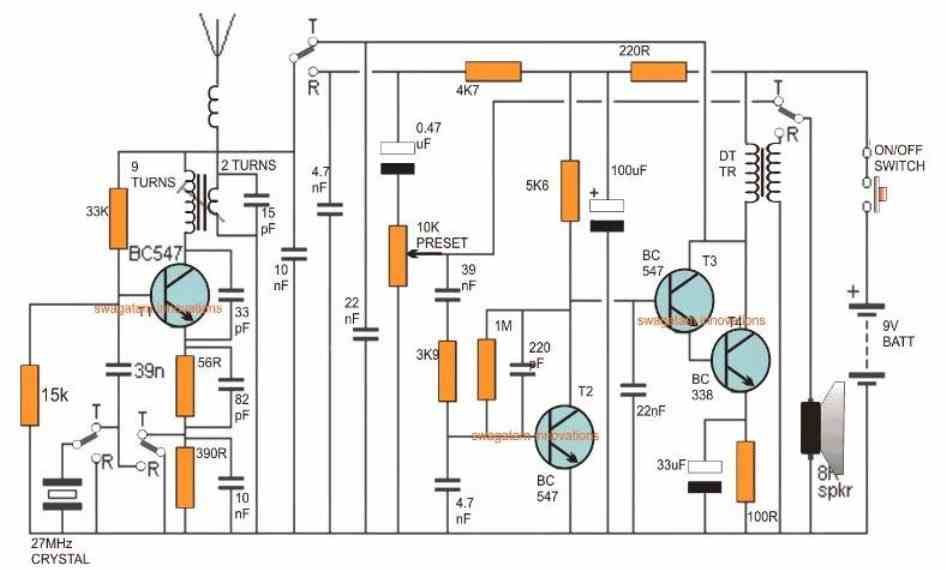

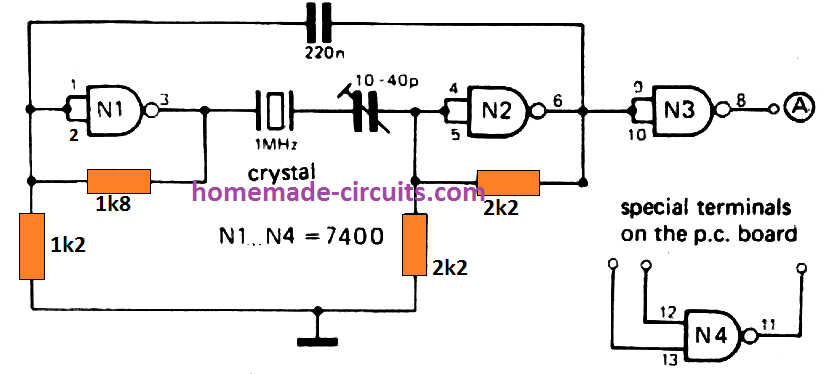

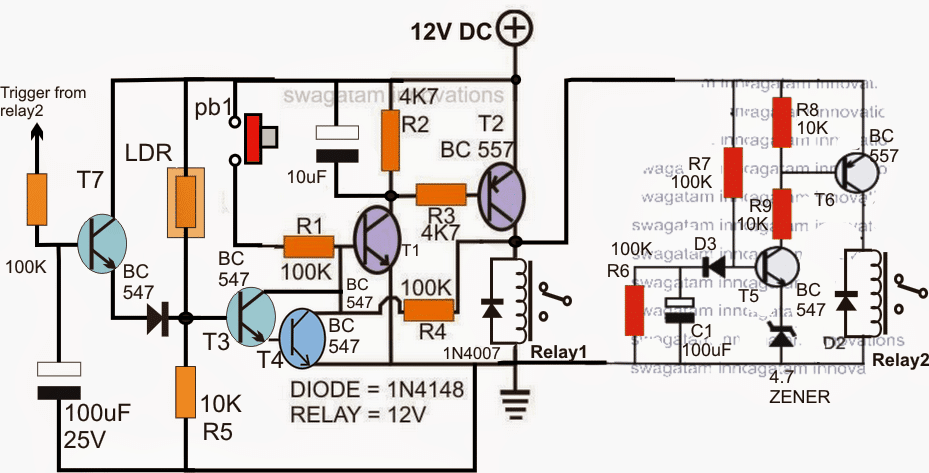

Unitat de control per cable

El disseny bàsic d’una unitat de control per cable es mostra més amunt. En aquest tipus, els senyals de control són generats per un maquinari especial circuit lògic sense cap canvi en l’estructura del circuit. En això, el senyal generat no es pot modificar per executar-lo al processador.

Les dades bàsiques d'un codi operatiu (el codi d'operació d'una instrucció s'envia al descodificador d'instruccions per descodificar-les. La instrucció descodificador és el conjunt de descodificadors per descodificar diferents tipus de dades en el codi op. Això dóna lloc a senyals de sortida que contenen valors de senyals actius que es donen com a entrada al generador de matrius per generar senyals de control per a l'execució d'un programa pel processador de l'ordinador.

Unitat de control basada en filferro

El generador de matrius proporciona els estats de la unitat de control i els senyals del processador (senyals d’interrupció). Matrix està construït com el matriu lògica programable . Els senyals de control generats pel generador de matrius es donen com a entrada a la següent matriu del generador i es combinen amb els senyals de temps de la unitat de temps que conté patrons rectangulars.

Per obtenir una nova instrucció, la unitat de control es converteix en una etapa inicial per a l'execució d'una nova instrucció. La unitat de control es manté a la fase inicial o primera fase sempre que els senyals de temporització, els senyals d’entrada i els estats d’instrucció d’un ordinador siguin invariables. El canvi d'estat de la unitat de control es pot augmentar si es produeix algun canvi en algun dels senyals generats.

Quan es produeix un senyal extern o una interrupció, la unitat de control passa al següent estat i realitza el processament del senyal d’interrupció. Els indicadors i estats s’utilitzen per seleccionar els estats desitjats per realitzar el cicle d’execució de la instrucció.

En l'últim estat, la unitat de control obté la següent instrucció i envia la sortida al comptador del programa, després al registre d'adreces de memòria, al registre de memòria intermèdia i al registre d'instruccions per llegir la instrucció. Finalment, si la darrera instrucció (que obté la unitat de control) és instrucció final, passa a l'estat de funcionament del processador i espera fins que l'usuari dirigeixi el següent programa.

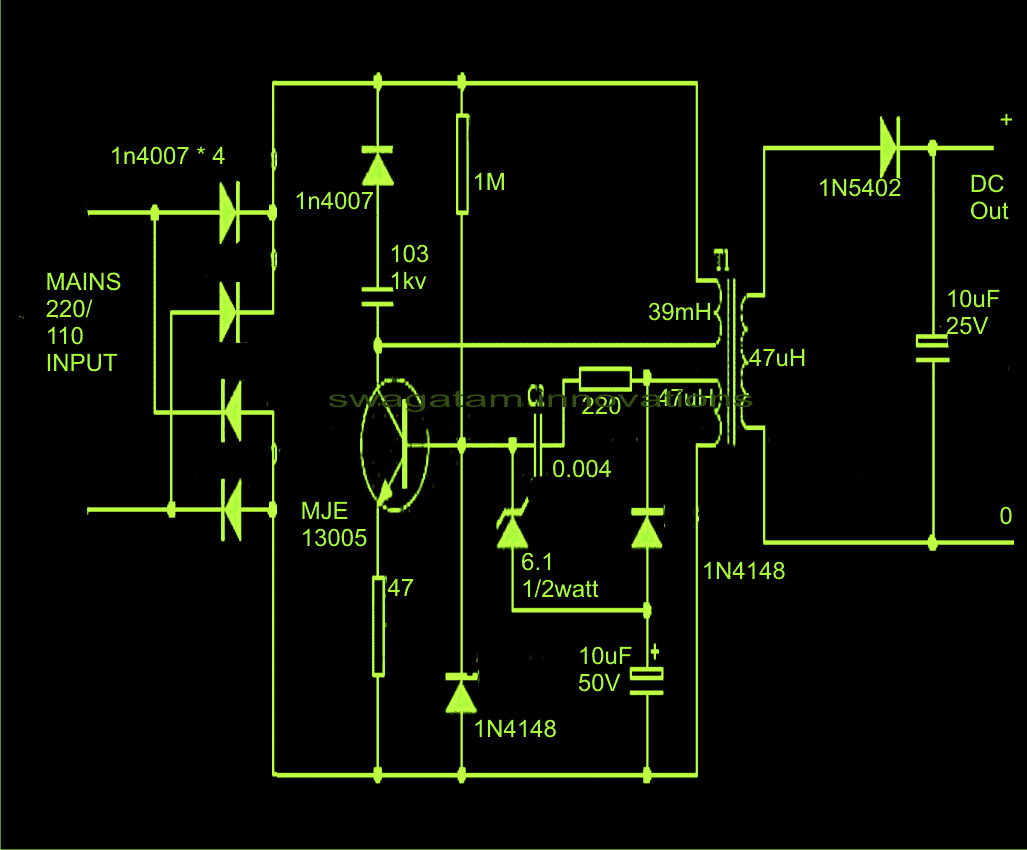

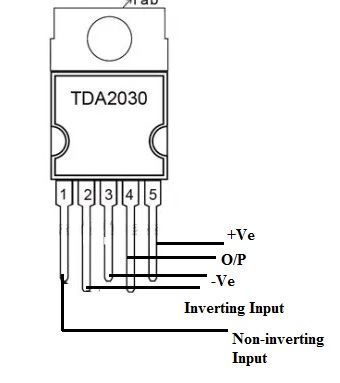

Unitat de control microprogramat

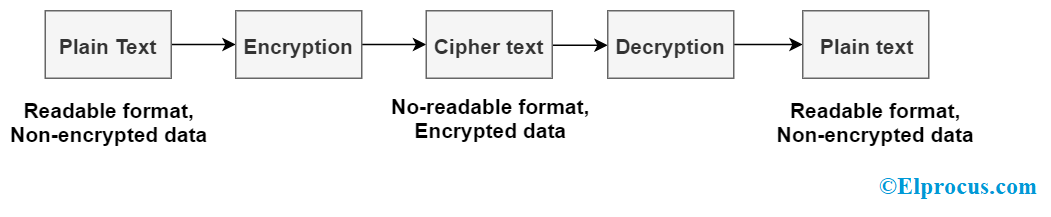

En aquest tipus, el magatzem de control s'utilitza per emmagatzemar els senyals de control que es codifiquen durant l'execució d'un programa. El senyal de control no es genera immediatament i es descodifica perquè el microprograma emmagatzema el camp d’adreça al magatzem de control. Tot el procés és d’un sol nivell.

Les microoperacions es realitzen per a l'execució de microinstruccions al programa. El diagrama de blocs de la unitat de control micro programada es mostra a la part superior. A partir del diagrama, l'adreça de la microinstrucció s'obté del registre d'adreces de memòria de control. Tota la informació de la unitat de control s’emmagatzema permanentment a la memòria de control anomenada ROM.

Unitat de control basada en microprogramació

La microinstrucció de la memòria de control la manté el registre de control. Atès que la microinstrucció té la forma de paraula de control (conté valors de control binaris) que necessita una o més microoperacions per realitzar el processament de dades.

Durant l'execució de microinstruccions, el següent generador d'adreces va calcular la següent adreça de la microinstrucció i, a continuació, l'envia al registre d'adreces de control per llegir la següent microinstrucció.

La seqüència de microoperacions d’un microprograma la realitza el següent generador d’adreces i actua com a seqüenciador de microprogrames per obtenir l’adreça de seqüència, és a dir, llegida des de la memòria de control.

Codi Verilog per a la unitat de control

A continuació es mostra el codi de Verilog per a la unitat de control.

`inclou' prj_definition.v '

mòdul Control_Unit (MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATA_R1, RF_DATA_R2, ALU_RESULT, zero, CLK, RST)

// Senyals de sortida

// Sortides per al fitxer de registre

sortida [`DATA_INDEX_LIMIT: 0] RF_DATA_W

sortida [`ADDRESS_INDEX_LIMIT: 0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

sortida RF_READ, RF_WRITE

// Sortides per ALU

sortida [`DATA_INDEX_LIMIT: 0] ALU_OP1, ALU_OP2

sortida [`ALU_OPRN_INDEX_LIMIT: 0] ALU_OPRN

// Sortides per a memòria

sortida [`ADDRESS_INDEX_LIMIT: 0] MEM_ADDR

sortida MEM_READ, MEM_WRITE

// Senyals d’entrada

entrada [`DATA_INDEX_LIMIT: 0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT

entrada ZERO, CLK, RST

// Senyal d’entrada

inout [`DATA_INDEX_LIMIT: 0] MEM_DATA

// Indiqueu les xarxes

wire [2: 0] proc_state

// manté el valor del comptador del programa, emmagatzema la instrucció actual, registra el punter de la pila

reg MEM_READ, MEM_WRITE

reg MEM_ADDR

reg ALU_OP1, ALU_OP2

reg ALU_OPRN

reg RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

reg RF_DATA_W

reg [1: 0] state, next_state

PROC_SM state_machine (.STATE (proc_state) ,. CLK (CLK) ,. RST (RST))

always @ (posedge CLK)

començar

si (RST)

estat<= RST

en cas contrari

estat<= next_state

final

sempre @ (estat)

començar

MEM_READ = 1’b0 MEM_WRITE = 1’b0 MEM_ADDR = 1’b0

ALU_OP1 = 1’b0 ALU_OP2 = 1’b0 ALU_OPRN = 1’b0

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0 RF_ADDR_W = 1’b0 RF_DATA_W = 1’b0

cas (estat)

`PROC_FETCH: comença

next_state = 'PROC_DECODE

MEM_READ = 1’b1

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0

RF_ADDR_W = 1’b1

final

`PROC_DECODE: començar

next_state = 'PROC_EXE

MEM_ADDR = 1’b1

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

MEM_WRITE = 1’b1

RF_ADDR_R1 = 1’b1 RF_ADDR_R2 = 1’b1

final

`PROC_EXE: comença

next_state = 'PROC_MEM

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

RF_ADDR_R1 = 1’b0

final

`PROC_MEM: comença

next_state = 'PROC_WB

MEM_READ = 1’b1 MEM_WRITE = 1’b0

final

`PROC_WB: comença

next_state = 'PROC_FETCH

MEM_READ = 1’b1 MEM_WRITE = 1’b0

final

endcase

final

endmodule

mòdul PROC_SM (STATE, CLK, RST)

// llista d’entrades

entrada CLK, RST

// llista de sortides

sortida [2: 0] ESTAT

// llista d’entrada

entrada CLK, RST

// llista de sortida

sortida ESTAT

reg [2: 0] ESTAT

estat reg [1: 0]

reg [1: 0] next_state

reg PC_REG, INST_REG, SP_REF

`definiu PROC_FETCH 3’h0

`definiu PROC_DECODE 3’h1

`definiu PROC_EXE 3’h2

`definiu PROC_MEM 3’h3

`definiu PROC_WB 3’h4

// iniciació d’estat

inicial

començar

estat = 2’bxx

next_state = 'PROC_FETCH

final

// restablir la gestió del senyal

always @ (posedge RST)

començar

state = 'PROC_FETCH

next_state = 'PROC_FETCH

final

always @ (posedge CLK)

començar

estat = estat_pròxim

final

sempre @ (estat)

començar

if (state === `PROC_FETCH)

començar

next_state = 'PROC_DECODE

print_instruction (INST_REG)

final

if (state === `PROC_DECODE)

començar

next_state = 'PROC_EXE

final

if (estat === `PROC_EXE)

començar

next_state = 'PROC_MEM

instrucció_impressió (SP_REF)

final

if (estat === `PROC_MEM)

començar

next_state = 'PROC_WB

final

if (estat === `PROC_WB)

començar

next_state = 'PROC_FETCH

instrucció_impressió (PC_REG)

final

final

tasca instrucció_impressió

entrada [`DATA_INDEX_LIMIT: 0] inst

reg [5: 0] opcode

reg [4: 0] rs

reg [4: 0] rt

reg [4: 0] rd

reg [4: 0] shamt reg [5: 0] funct reg [15: 0] reg immediat [25: 0] adreça

començar

// analitzeu la instrucció

// tipus R

{opcode, rs, rt, rd, shamt, funct} = inst

// Escric jo

{opcode, rs, rt, immediat} = inst

// tipus J

{opcode, address} = inst

$ write ('@% 6dns -> [0X% 08h]', $ time, inst)

cas (opcode) // R-Type

6'h00: inici

cas (funció)

6’h20: $ write ('afegir r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h22: $ write ('sub r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h2c: $ write ('mul r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h24: $ write ('i r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h25: $ write ('or r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h27: $ write ('ni r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h2a: $ write ('slt r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h00: $ write ('sll r [% 02d],% 2d, r [% 02d]', rs, shamt, rd)

6’h02: $ write ('srl r [% 02d], 0X% 02h, r [% 02d]', rs, shamt, rd)

6’h08: $ write ('jr r [% 02d]', rs)

per defecte: $ write ('')

endcase

final

// Escric jo

6’h08: $ write ('addi r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediat)

6’h1d: $ write ('muli r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediat)

6’h0c: $ write ('andi r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediat)

6’h0d: $ write ('ori r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediat)

6’h0f: $ write ('lui r [% 02d], 0X% 04h', rt, immediat)

6’h0a: $ write ('slti r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediat)

6’h04: $ write ('beq r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediat)

6’h05: $ write ('bne r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediat)

6’h23: $ write ('lw r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediat)

6’h2b: $ write ('sw r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediat)

// Tipus J

6’h02: $ write ('jmp 0X% 07h', adreça)

6’h03: $ write ('jal 0X% 07h', adreça)

6’h1b: $ write ('push')

6’h1c: $ write ('pop')

per defecte: $ write ('')

endcase

$ write (' n')

final

tasca final

mòdul final

Preguntes freqüents

1). Quina és la feina d'una unitat de control?

El treball de la unitat de control és dirigir el flux de dades o instruccions per a l'execució pel processador d'un ordinador. Controla, gestiona i coordina les unitats de memòria principal, ALU, registres, entrades i sortides. Obté les instruccions i genera senyals de control per a l'execució.

2). Què és la memòria de control?

La memòria de control sol ser RAM o ROM per emmagatzemar l'adreça i les dades del registre de control.

3). Què és la unitat de control de Wilkes?

El seqüencial i circuits combinacionals de la unitat de control per cable es reemplacen per la unitat de control de Wilkes. Utilitza una unitat d’emmagatzematge per emmagatzemar les seqüències d’instruccions d’un microprograma.

4). Què és una unitat de control per cable?

La unitat de control per cable genera els senyals de control canviant d’un estat a un altre en cada impuls de rellotge sense cap canvi físic al circuit. La generació de senyals de control depèn del registre d’instruccions, del descodificador i dels senyals d’interrupció.

5). Què és la memòria de control?

La informació de la unitat de control o les dades s’emmagatzemen temporalment o permanentment a la memòria de control.

La memòria de control és de dos tipus. Són memòries d'accés aleatori (RAM) i memòria de només lectura (ROM).

Per tant, es tracta de la definició, components, disseny, diagrama, funcions i tipus d’unitat de control . Aquí teniu una pregunta: 'Quin és el propòsit del registre d'adreces de control?'