El transistor MOS és l'element més fonamental en el disseny de circuits integrats a gran escala. Aquests transistors es classifiquen generalment en dos tipus PMOS i NMOS. La combinació de transistors NMOS i PMOS es coneix com a Transistor CMOS . El diferent portes lògiques i altres dispositius lògics digitals implementats han de tenir lògica PMOS. Aquesta tecnologia és barata i té una bona resistència a les interferències. Aquest article tracta sobre un dels tipus de transistors MOS com un transistor PMOS.

Què és el transistor PMOS?

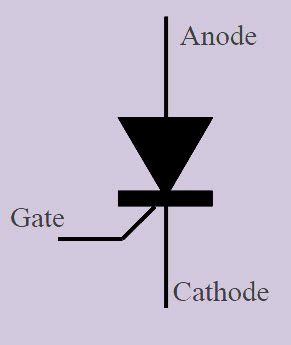

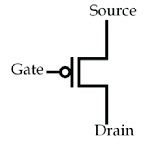

El transistor PMOS o semiconductor d'òxid metàl·lic de canal P és una mena de transistor on els dopants de tipus p s'utilitzen a la regió del canal o de la porta. Aquest transistor és exactament el contrari del transistor NMOS. Aquests transistors tenen tres terminals principals; la font, la porta i el drenatge on la font del transistor està dissenyada amb un substrat de tipus p, i el terminal de drenatge està dissenyat amb un substrat de tipus n. En aquest transistor, els portadors de càrrega com els forats són els responsables de la conducció del corrent. Els símbols del transistor PMOS es mostren a continuació.

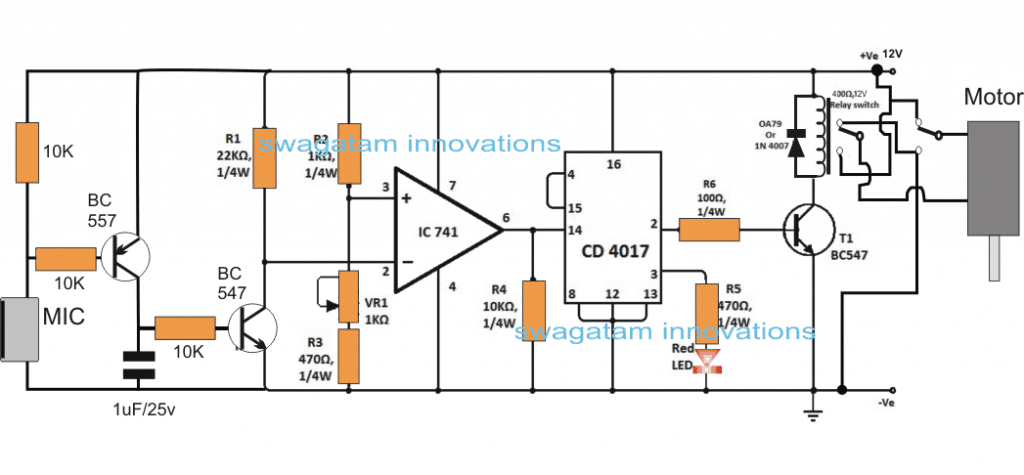

Com funciona el transistor PMOS?

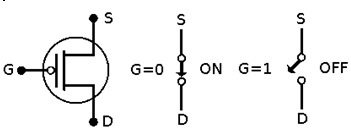

El funcionament del transistor de tipus p és força oposat al transistor de tipus n. Aquest transistor formarà un circuit obert sempre que obtingui una tensió no menyspreable, cosa que significa que no hi ha flux d'electricitat des del terminal de la porta (G) fins a la font (S). De la mateixa manera, aquest transistor forma un circuit tancat quan obté una tensió al voltant de 0 volts, el que significa que el corrent flueix des del terminal de la porta (G) fins al drenatge (D).

Aquesta bombolla també es coneix com a bombolla d'inversió. Per tant, la funció principal d'aquest cercle és invertir el valor de la tensió d'entrada. Si el terminal de la porta proporciona una tensió 1, aquest inversor el canviarà a zero i funcionarà el circuit en conseqüència. Per tant, la funció del transistor PMOS i del transistor NMOS és força oposada. Un cop els fusionem en un únic circuit MOS, es convertirà en un circuit CMOS (semiconductor complementari d'òxid metàl·lic).

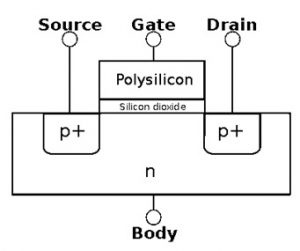

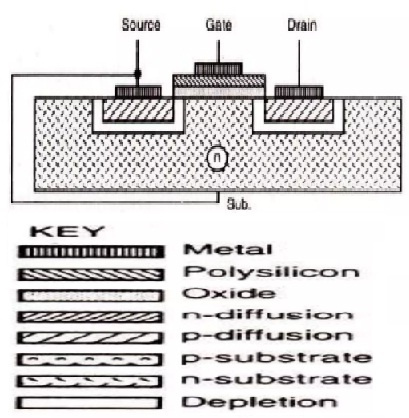

Secció transversal del transistor PMOS

A continuació es mostra la secció transversal del transistor PMOS. Un transistor pMOS està construït amb un cos de tipus n que inclou dues regions de semiconductors de tipus p adjacents a la porta. Aquest transistor té una porta de control tal com es mostra al diagrama que controla el flux d'electrons entre els dos terminals com la font i el drenatge. Al transistor pMOS, el cos es manté a +ve voltatge. Una vegada que el terminal de la porta és positiu, els terminals d'origen i de drenatge estan esbiaixats inversament. Un cop això succeeix, no hi ha flux de corrent, de manera que el transistor s'apagarà.

Un cop baixi el subministrament de tensió al terminal de la porta, els portadors de càrrega positiva seran atrets a la part inferior de la interfície Si-SiO2. Sempre que la tensió baixi prou, el canal s'invertirà i crearà un camí conductor des del terminal font fins al drenatge permetent el flux de corrent.

Sempre que aquests transistors tracten amb lògica digital, solen tenir dos valors diferents només com 1 i 0 (ON i OFF). La tensió positiva del transistor es coneix com a VDD, que representa el valor lògic alt (1) dins dels circuits digitals. Els nivells de tensió del VDD Lògica TTL generalment eren al voltant dels 5V. En l'actualitat, els transistors no poden suportar tensions tan altes perquè normalment oscil·len entre 1,5 V i 3,3 V. La baixa tensió es coneix sovint com a GND o VSS. Per tant, VSS significa el '0' lògic i també s'estableix normalment a 0V.

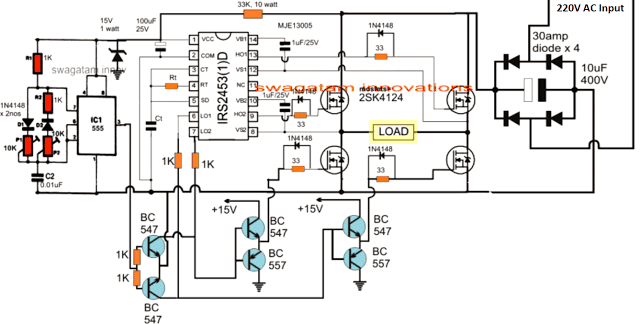

Circuit de transistors PMOS

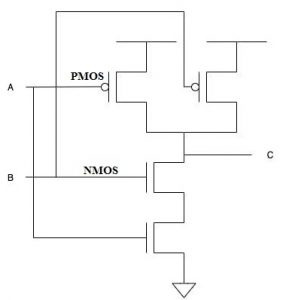

A continuació es mostra el disseny de la porta NAND que utilitza el transistor PMOS i el transistor NMOS. En general, una porta NAND en electrònica digital és una porta lògica que també s'anomena porta NOT-AND. La sortida d'aquesta porta és baixa (0) només si les dues entrades són altes (1) i la seva sortida és un complement d'una porta AND. Si alguna de les dues entrades és BAIX (0), dóna resultats de sortida alts.

Al circuit lògic següent, si l'entrada A és 0 i B és 0, llavors una entrada de pMOS produirà '1' i una entrada de nMOS produirà '0'. Per tant, aquesta porta lògica genera un '1' lògic perquè està connectada a la font mitjançant un circuit tancat i deslligada de la GND a través d'un circuit obert.

Quan A és '0' i B' és '1', llavors una entrada de pMOS generarà un '1' i una entrada de NMOS generarà un '0'. Així, aquesta porta en produirà una de lògica perquè està connectada a la font mitjançant un circuit tancat i deslligada de la GND per un circuit obert. Quan A és '1' i B és '0', aleshores l'entrada 'B' de pMOS generarà una sortida alta (1) i l'entrada 'B' de NMOS generarà una sortida tan baixa (0). Per tant, aquesta porta lògica generarà un 1 lògic perquè està connectada a la font mitjançant un circuit tancat i deslligada de la GND per un circuit obert.

Quan A és '1' i B és '1', llavors una entrada de 'pMOS produirà un zero i una entrada de nMOS generarà '1'. En conseqüència, també hauríem de verificar l'entrada B de pMOS i nMOS. L'entrada B de pMOS generarà un '0' i l'entrada B de nMOS generarà un '1'. Per tant, aquesta porta lògica generarà un '0' lògic perquè està deslligada de la font per un circuit obert i està connectada a GND mitjançant un circuit tancat.

Taula de la Veritat

A continuació es mostra la taula de veritat del circuit lògic anterior.

|

A |

B |

C |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

La tensió de llindar del transistor PMOS és normalment el 'Vgs', que és necessari per crear el canal conegut com a inversió de canal. En un transistor PMOS, el substrat i els terminals font simplement estan connectats a 'Vdd'. Si comencem a reduir la tensió per referència al terminal d'origen al terminal de la porta des de Vdd fins a un punt on noteu la inversió del canal, en aquesta posició, si analitzeu que Vgs i la font estan a un alt potencial, obtindreu un valor negatiu. Per tant, el transistor PMOS té un valor V negatiu.

Procés de fabricació de PMOS

Els passos implicats en la fabricació de transistors PMOS es discuteixen a continuació.

Pas 1:

Una fina capa d'hòsties de silici es converteix en material de tipus N simplement dopant material de fòsfor.

Pas 2:

Es cultiva una capa gruixuda de diòxid de silici (Sio2) sobre un substrat complet de tipus p.

Pas 3:

Ara la superfície està recoberta amb un fotoresistent sobre la gruixuda capa de diòxid de silici.

Pas 4:

Després d'això, aquesta capa simplement s'exposa a la llum UV a través d'una màscara que defineix aquelles regions a les quals s'ha de produir la difusió juntament amb els canals de transistors.

Pas 5:

Aquestes regions estan gravades mútuament amb el diòxid de silici subjacent de manera que la superfície de l'hòstia quedi exposada dins de la finestra definida per la màscara.

Pas 6:

La fotoresistència restant es desprèn i la capa fina de Sio2 es cultiva normalment 0,1 micròmetres sobre tota la superfície del xip. Després d'això, es col·loca polisilici per formar l'estructura de la porta. Es col·loca un fotoresistent sobre tota la capa de polisilici i exposa la llum UV a través de la màscara2.

Pas 7:

Les difusions s'aconsegueixen mitjançant l'escalfament de les hòsties a la temperatura màxima i el pas de gas amb impureses de tipus p desitjades com el bor.

Pas 8:

Es fa créixer un diòxid de silici d'1 micròmetre de gruix i s'hi diposita material fotoresistent. Exposeu la llum ultraviolada amb màscara3 a les zones preferides de la porta, la font i el desguàs que estan gravades per fer els talls de contacte.

Pas 9:

Ara un metall o alumini es diposita sobre la seva superfície d'1 micròmetre de gruix. Un cop més, es cultiva un material fotoresistent per tot el metall i exposa la llum UV a través de la màscara4 que es grava per formar el disseny d'interconnexió necessari. L'estructura PMOS final es mostra a continuació.

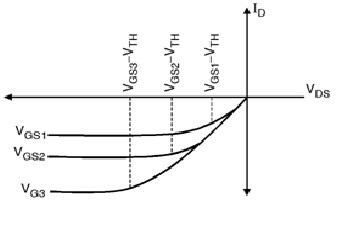

Característiques del transistor PMOS

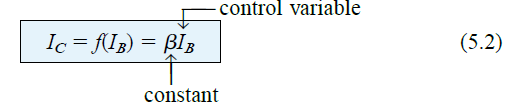

Les característiques I-V del transistor PMOS es mostren a continuació. Aquestes característiques es divideixen en dues regions per tal d'obtenir la relació entre el corrent de drenatge a la font (I DS), així com les seves tensions terminals com les regions lineals i de saturació.

En una regió de revestiment, l'IDS augmentarà linealment quan s'augmenta el VDS (tensió de drenatge a la font), mentre que a la regió de saturació, l'I DS és estable i és independent del VDS. La relació principal entre l'ISD (font per drenar el corrent) i les seves tensions terminals es deriva mitjançant un procediment similar del transistor NMOS. En aquest cas, l'únic canvi serà que els portadors de càrrega presents a la capa d'inversió són simplement forats. Quan els forats es mouen de la font al desguàs, el flux de corrent també és el mateix.

Així, el signe negatiu apareix dins de l'equació actual. A més, tots els biaixos aplicats als terminals del dispositiu són negatius. Per tant, les característiques ID - VDS del transistor PMOS es mostren a continuació.

L'equació de corrent de drenatge per al transistor PMOS a la regió lineal es dóna com:

ID = – mp Cox

De la mateixa manera, l'equació de corrent de drenatge per al transistor PMOS a la regió de saturació es dóna com:

ID = – mp Cox (VSG – | V TH |p )^2

On 'mp' és la mobilitat del forat i '|VTH| p' és la tensió de llindar del transistor PMOS.

A l'equació anterior, el signe negatiu indicarà que l'ID( corrent de drenatge ) flueix des del desguàs (D) a la font (S), mentre que els forats flueixen en sentit contrari. Quan la mobilitat del forat és baixa en comparació amb la mobilitat d'electrons, els transistors PMOS pateixen la capacitat de la unitat de baix corrent.

Per tant, es tracta d'una visió general del transistor PMOS o del transistor mos de tipus p: fabricació, circuit i el seu funcionament. PMOS els transistors estan dissenyats amb una font p, un substrat n i drenatge. Els portadors de càrrega de PMOS són forats. Aquest transistor condueix una vegada que s'aplica baixa tensió al terminal de la porta. Els dispositius basats en PMOS són menys propensos a interferències en comparació amb els dispositius NMOS. Aquests transistors es poden utilitzar com a resistències controlades per tensió, càrregues actives, miralls de corrent, amplificadors d'impedància trans, i també s'utilitzen en interruptors i amplificadors de tensió. Aquí teniu una pregunta per a vosaltres, què és un transistor NMOS?