En el nostre dia a dia, ens trobem amb diversos tipus d’aparells electrònics. Una de les tecnologies que va provocar una revolució en la producció d’electrònica és “ Circuit integrat “. Aquesta tecnologia va reduir la mida dels productes electrònics augmentant la densitat de portes lògiques per xip. Avui en dia tenim diferents tipus i configuracions d’IC. Com observem al voltant, trobem que alguns circuits integrats només es poden utilitzar per a una aplicació específica, mentre que alguns IC es poden reprogramar i utilitzar per a diverses aplicacions. Aquest tipus d’IC s’anomenen ASIC. Però, en què es diferencien? Com és possible reprogramar-los? Per què algunes IC no es poden reprogramar? Seguiu buscant respostes a aquestes preguntes.

Què és un ASIC (Circuit integrat específic de l'aplicació)?

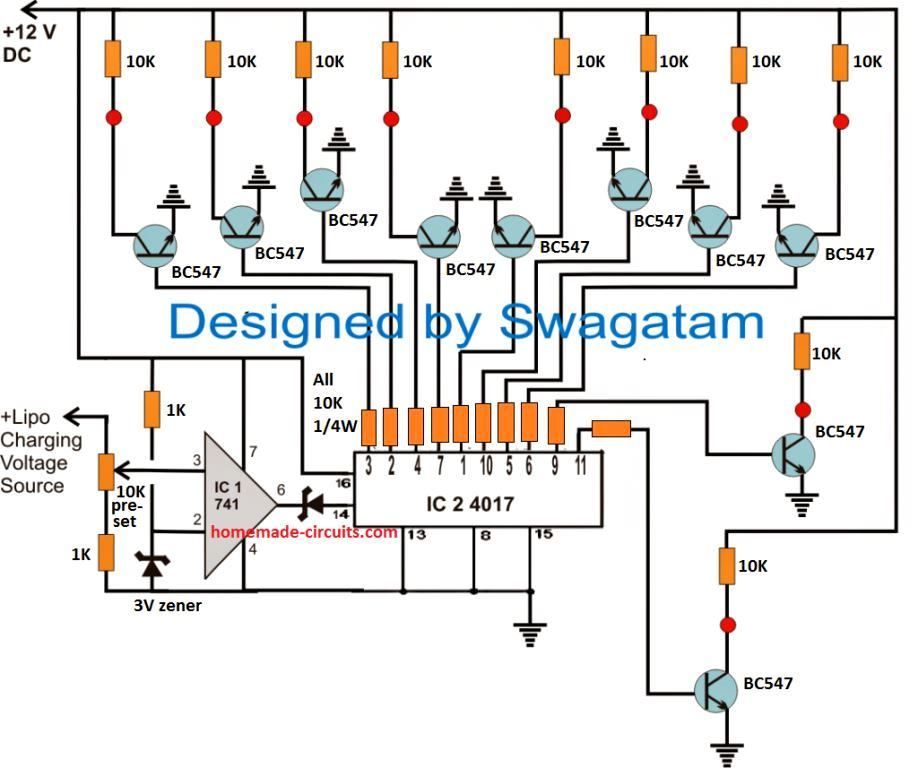

El formulari complet ASIC és Circuit integrat específic de l'aplicació. Aquests circuits són específics de l’aplicació, és a dir. ICs fets a mida per a una aplicació concreta. Normalment es dissenyen des del nivell arrel en funció del requisit de l'aplicació en particular. Alguns dels bàsics exemples de circuits integrats específics de l'aplicació són xips utilitzats en joguines, el xip utilitzat per a la interfície de memòria i microprocessador, etc. Aquests xips només es poden utilitzar per a aquella aplicació per a la qual estan dissenyats. Presumiblement, aquestes tipus d’IC només es prefereixen per a aquells productes que tinguin una gran producció. Com que els ASIC estan dissenyats des del nivell arrel, tenen un cost elevat i només es recomanen per a produccions de gran volum.

El principal avantatge d'ASIC és la mida reduïda del xip ja que un gran nombre d'unitats funcionals d'un circuit es construeixen sobre un sol xip. L’ASIC modern inclou generalment un 32-bit microprocessador , blocs de memòria, circuits de xarxa, etc. Aquest tipus d'ASIC es coneix com Sistema al xip . Amb el desenvolupament de la tecnologia de fabricació i l’augment de la investigació en mètodes de disseny, es desenvolupen ASIC amb diferents nivells de personalització.

Tipus d’ASIC

Els ASIC es classifiquen en funció de la quantitat de personalització que un programador pot fer en un xip.

Tipus d’ASIC

Personalitzat complet

En aquest tipus de disseny, totes les cel·les lògiques estan dissenyades per a aplicacions específiques, és a dir. el dissenyador ha de fer especialment les cel·les lògiques dels circuits. Es personalitzen totes les capes de màscara per a la interconnexió. Per tant, el programador no pot canviar les interconnexions del xip i, mentre programa, ha de ser conscient de la disposició del circuit.

Un dels millors exemples d'ASIC personalitzat complet és un microprocessador. Aquest tipus de personalització permet als dissenyadors construir diversos circuits analògics, cèl·lules de memòria optimitzades o estructures mecàniques en un sol CI. Aquest ASIC és costós i requereix molt de temps de fabricació i disseny. El temps que es triga a dissenyar aquests CI és d’unes vuit setmanes.

Normalment estan pensats per a aplicacions d’alt nivell. Les funcions principals del disseny personalitzat complet són el màxim rendiment, l’àrea minimitzada i el màxim grau de flexibilitat. Finalment, el risc és elevat en el disseny, ja que les cèl·lules lògiques, la resistència, etc. Els elements del circuit utilitzats no es pretenen.

Semi-personalitzat

En aquest tipus de lògica de disseny, les cel·les s’extreuen de les biblioteques estàndard, és a dir. no estan fets a mà com en el disseny personalitzat complet. Algunes màscares es personalitzen mentre que altres es prenen de la biblioteca predissenyada. Basant-se en el tipus de cel·les lògiques preses de la biblioteca i la quantitat de personalització permesa per a les interconnexions, aquests ASIC es divideixen en dos tipus: ASIC basats en cel·les estàndard i ASIC basats en Gate Array.

1). ASIC estàndard basat en cèl·lules

Per conèixer aquestes IC primer, entenem què significa una biblioteca de cel·les estàndard. Algunes de les cel·les lògiques com AND portes, O portes , multiplexors, xancletes estan predissenyats per dissenyadors mitjançant diferents configuracions, estandarditzades i emmagatzemades en forma de biblioteca. Aquesta col·lecció es coneix com a biblioteca de cel·les estàndard.

ASIC estàndard basat en cèl·lules

En cèl·lules lògiques ASIC basades en cèl·lules estàndard s’utilitzen aquestes biblioteques estàndard. Al xip ASIC, l'àrea de cel·la estàndard o bloc flexible es compon de cel·les estàndard disposades en forma de files. Juntament amb aquests blocs flexibles, s'utilitzen mega cèl·lules com microcontroladors o fins i tot microprocessadors al xip. Aquestes mega cèl·lules també es coneixen com a funcions Mega, macros de nivell de sistema, blocs fixos, blocs estàndard funcionals.

La figura superior representa una cèl·lula ASIC estàndard amb una única àrea de cèl·lula estàndard i quatre blocs fixos. Les capes de màscara es personalitzen. Aquí el dissenyador pot col·locar cel·les estàndard en qualsevol lloc del dau. Aquests també es coneixen com a C-BIC.

2). Porta ASIC basada en matriu

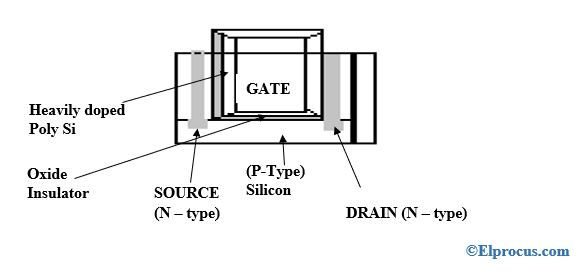

Aquest tipus d'ASIC semi-personalitzats s'han predefinit transistors a l'hòstia de silici, és a dir. el dissenyador no pot canviar la ubicació dels transistors presents a la matriu. La matriu base és el patró predefinit de la matriu de portes i la cel·la base és la cel·la repetitiva més petita de la matriu base.

El dissenyador només té la responsabilitat de canviar la interconnexió entre transistors mitjançant les primeres capes metàl·liques de la matriu. El dissenyador tria entre la biblioteca de matrius de portes. Sovint s’anomenen matrius de portes enmascarades. Els ASIC basats en matrius de porta són de tres tipus. Són matrius de porta canalitzada, matriu de portes sense canal i una matriu de portes estructurada.

a) .Canaled Gate Array

En aquest tipus de matriu de portes, es deixa espai de cablejat entre files de transistors. Són similars a CBIC, ja que es deixa espai per a la interconnexió entre blocs, però a les files de cel·les de la matriu de portes canalitzades es fixen en alçada, mentre que a CBIC es pot ajustar aquest espai.

Matriu de porta canalitzada

Algunes de les característiques principals d’aquest array de portes són: aquest array de portes utilitza espais predefinits entre files per a la interconnexió. El temps de fabricació és de dos dies a dues setmanes.

b). Arran de porta de canal menys canal

No queda espai lliure per encaminar entre files de cel·les tal com es veu a la matriu de portes canalitzades. Aquí l’encaminament es fa des de sobre les cel·les de la matriu de la porta ja que podem personalitzar la connexió entre el metall 1 i els transistors. Per al routing, deixem els transistors estirats en el camí de routing sense utilitzar. El termini de fabricació és d’unes dues setmanes.

Arran de porta de canal menys canal

c). Matriu de portes estructurades

Aquest tipus de matriu de portes té un bloc incrustat juntament amb files de matriu de portes, tal com es va veure més amunt. La matriu de portes estructurades té una major eficiència de l'àrea de CBIC. Igual que la matriu de portes emmascarades, aquestes tenen un cost més baix i una resposta més ràpida. Aquí la mida fixa de la funció incrustada suposa una limitació a la matriu de portes estructurades. Per exemple, aquesta matriu de portes conté una àrea reservada per al controlador de 32 k bits, però si en una aplicació només necessitem una àrea per al controlador de 16 k bits, es perd la zona restant. Totes les matrius de portes tenen un temps de resposta de dos dies a dues setmanes tots tenen interconnexió personalitzada.

Matriu de portes estructurades

ASIC programable

Hi ha dos tipus d’ASIC programables. Són PLD i FPGA

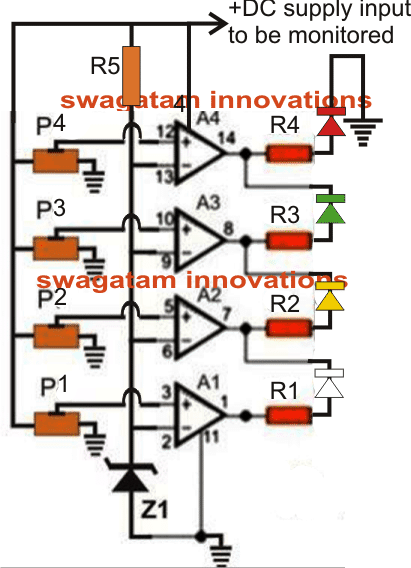

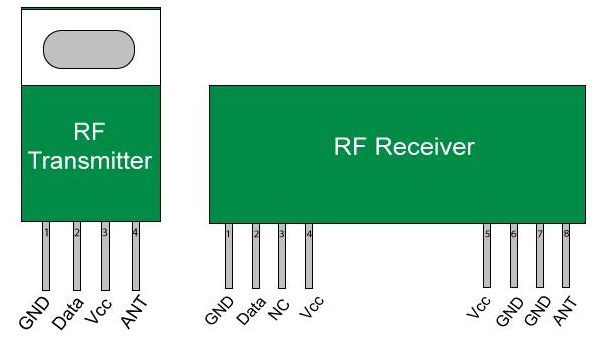

PLD (Dispositius lògics programables)

Aquestes són les cel·les estàndard disponibles fàcilment. Podem programar un PLD per personalitzar una part de l’aplicació, de manera que es considerin ASIC. Podem utilitzar diferents mètodes i programes per programar un PLD. Aquests contenen una matriu regular de cèl·lules lògiques generalment lògica de matriu programable juntament amb xancles o pestells. Aquí hi ha interconnexions com un sol bloc gran.

PROM és un exemple habitual d’aquest CI. EPROM utilitza transistors MOS com a interconnexió, de manera que aplicant alta tensió el podem programar. Els PLD no tenen cap cel·la lògica ni interconnexió personalitzada. Aquests tenen un canvi de disseny ràpid.

Dispositius lògics programables

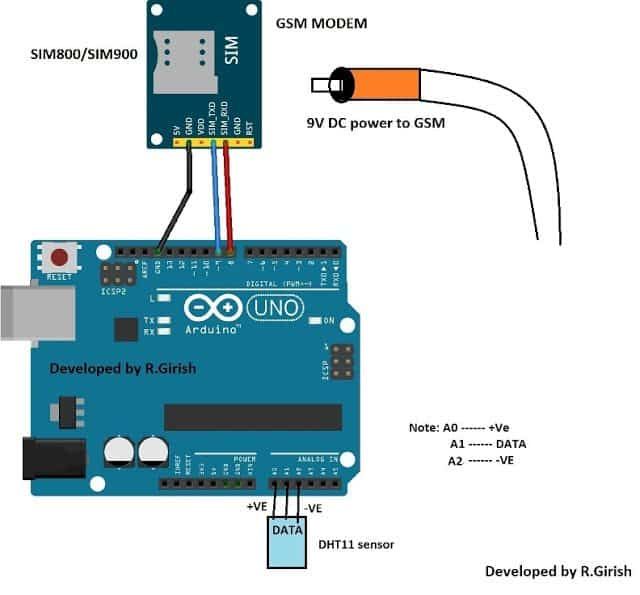

FPGA (Field Programmable Gate Array)

On els PLD tenen una lògica de matriu programable com a cel·les lògiques FPGA té un arranjament semblant a un array. Els PLD són més petits i menys complexos que els FPGA. A causa de la seva flexibilitat i característiques, FPGA està substituint TTL en sistemes microelectrònics. El canvi de disseny és de poques hores.

Matriu de portes programables de camp

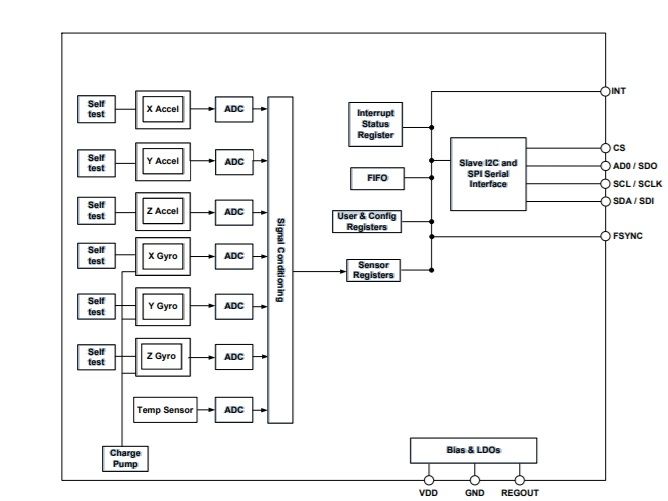

El nucli consisteix en cèl·lules lògiques bàsiques programables que poden realitzar totes dues combinacional i lògica seqüencial . Podem programar cel·les lògiques i interconnectar-nos mitjançant alguns mètodes. Les cel·les lògiques bàsiques estan envoltades per la matriu d'interconnexions programables i el nucli està envoltat per cel·les d'E / S programables.

FPGA sol estar format per blocs lògics configurables, blocs d'E / S configurables, interconnexions programables, circuits de rellotge, ALU, memòria, descodificadors.

Hem vist els diferents tipus d’ASIC disponibles. Ara entenem quan es fan totes aquestes personalitzacions i interconnexions durant la fabricació.

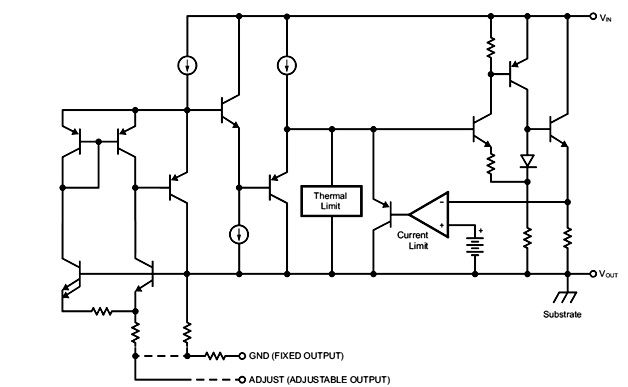

Flux de disseny de circuits integrats específics d'aplicació (ASIC)

Dissenyar un ASIC es realitza pas a pas. Aquest ordre de passos es coneix com Disseny ASIC Flux. A continuació es mostren els passos del flux de disseny.

Flux de disseny ASIC

Entrada de disseny: En aquest pas, la microarquitectura del disseny s’implementa mitjançant llenguatges de descripció de maquinari com VHDL, Verilog i System Verilog.

Síntesi lògica: En aquest pas es prepara una llista de xarxes de cel·les lògiques que s'utilitzaran, tipus d'interconnexions i totes les altres parts necessàries per a l'aplicació mitjançant HDL.

Particionament del sistema: En aquest pas, dividim el troquel de mida gran en peces de mida ASIC.

Simulació prèvia al disseny: En aquest pas, es fa una prova de simulació per comprovar si el disseny conté errors.

Planificació del sòl: En aquest pas, es disposen blocs de netlist al xip.

Col·locació: En aquest pas es decideix la ubicació de les cel·les dins del bloc.

Encaminament: En aquest pas, es dibuixen connexions entre blocs i cel·les. Extracció: en aquest pas, determinem les propietats elèctriques com el valor de resistència i el valor de la capacitat d’interconnexió.

Simulació posterior al disseny: Abans de l'enviament del model per a la fabricació, aquesta simulació es fa per comprovar si el sistema funciona correctament juntament amb una càrrega d'interconnexió.

Exemples d'ASIC

Després d’haver conegut les diferents característiques d’ASIC ara anem a veure alguns exemples d’ASIC.

ASIC estàndard basat en cèl·lules: LCB 300k, 500k de LSI Logic Company, SIG1, 2, 3 famílies de ABB Hafo Inc., GCS90K de GCS Plessey.

Productes Gate Array: AUA20K de Harris Semiconductor, SCX6Bxx de National Semiconductors, famílies TGC / TEC de Texas Instruments.

Productes PLD: Família PAL de Micro Devices avançats, família GAL de Philips Semiconductors, XC7300 i EPLD de XILINX.

Productes FPGA: XC2000, XC3000, XC4000, sèries XC5000 de XILINX, pASIC1 de QuickLogic, MAX5000 d’Altera.

Aplicacions d'ASIC

La singularitat d’ASIC ha revolucionat la manera de fabricar l’electrònica. Això va reduir les mides de matrius alhora que va augmentar la densitat de portes lògiques per xip. Els ASIC solen ser els preferits per a aplicacions d’alt nivell. El xip ASIC s’utilitza com a nuclis IP per a satèl·lits, fabricació de ROM, Microcontrolador i diversos tipus d'aplicacions en els sectors mèdic i de recerca. Una de les aplicacions de moda d’ASIC és BITCOIN MINER.

Bitcoin Miner

La mineria de criptomonedes requereix maquinari d’alta potència i alta velocitat. Una CPU de propòsit general no pot proporcionar una capacitat de càlcul tan alta a gran velocitat. Els miners de bitcoins ASIC són xips integrats en plaques base i dissenyats especialment fonts d'alimentació , construït en una sola unitat. És un maquinari dissenyat a propòsit fins al nivell de xip per a la mineria de bitcoins. Aquestes unitats només poden executar l'algorisme d'una sola criptomoneda. Presumiblement, per a un tipus de criptomoneda diferent, necessitem un altre miner.

Avantatges i desavantatges d'ASIC

El avantatges d'ASIC inclou el següent.

- La petita mida d'ASIC el converteix en una opció molt elevada per a sistemes més grans i sofisticats.

- Com que hi ha un gran nombre de circuits construïts sobre un sol xip, això provoca aplicacions d'alta velocitat.

- ASIC té un baix consum d'energia.

- Com que són el sistema del xip, els circuits estan presents un al costat de l’altre. Per tant, cal un encaminament mínim per connectar diversos circuits.

- ASIC no té problemes de temps i configuració de postproducció.

El desavantatges d’ASIC inclou el següent.

- Com que són xips personalitzats, proporcionen poca flexibilitat per a la programació.

- Com que aquests xips s'han de dissenyar des del nivell arrel, tenen un cost per unitat elevat.

- ASIC té més temps per comercialitzar el marge.

ASIC vs FPGA

La diferència entre ASIC i FPGA inclou el següent.

ASIC | FPGA |

| No reprogramable | Reprogramable |

| Preferit per a produccions de gran volum | Preferit per a produccions de baix volum |

| Són aplicacions específiques | S'utilitza com a prototips d'un sistema |

| L’eficiència energètica requereix menys energia | Menys eficiència energètica requereix més energia |

| Es tracta de circuits permanents que no es poden actualitzar de tant en tant. | Molt adequat per a aplicacions on el circuit ha de ser actualitzat de tant en tant com xips de telèfons mòbils, estacions base, etc. |

Per tant, es tracta d’una visió general de Circuit integrat específic de l'aplicació . La invenció de l'ASIC ha provocat un canvi enorme en la manera d'utilitzar l'electrònica. Utilitzem ASIC en la nostra vida diària en forma de diverses aplicacions. Quines aplicacions d'ASIC heu trobat? Amb quin tipus d’ASIC heu treballat?