Les funcions més poderoses i importants són les interrupcions a Microcontrolador 8051 . En la majoria dels processos en temps real, per gestionar certes condicions correctament, la tasca real s’ha d’aturar durant algun temps (es fa l’acció necessària) i després ha de tornar a la tasca principal. Per executar aquest tipus de programes, són necessàries les interrupcions. Es diferencia completament del mètode de votació en què el processador ha de comprovar seqüencialment cada dispositiu i preguntar si el servei és necessari o no mentre consumeix més temps del processador.

Interromp en el microcontrolador 8051

Les interrupcions del microcontrolador 8051 són més desitjables per reduir la comprovació regular de l'estat dels dispositius interfaces o dispositius integrats. La interrupció és un esdeveniment que suspèn temporalment el programa principal, passa el control a una secció de codi especial, executa la funció relacionada amb l'esdeveniment i reprèn el flux del programa principal on l'havia deixat.

Les interrupcions són de diferents tipus, com ara programari i maquinari, emmascarables i no emmascarables, interrupcions fixes i vectorials, etc. La rutina de servei d’interrupció (ISR) apareix a la imatge quan es produeix una interrupció i, a continuació, indica al processador que prengui les mesures adequades per a la interrupció i, després de l’execució d’ISR, el controlador salta al programa principal.

Tipus d'interrupcions en el microcontrolador 8051

El microcontrolador 8051 pot reconèixer cinc esdeveniments diferents que fan que el programa principal s'interrompi des de l'execució normal. Aquestes cinc fonts d'interrupcions el 8051 són:

- Interrupció de desbordament del temporitzador 0: TF0

- Interrupció de desbordament del temporitzador 1: TF1

- Interrupció de maquinari extern- INT0

- Interrupció de maquinari extern- INT1

- Interrupció de comunicació sèrie- RI / TI

Les interrupcions temporitzadores i de sèrie són generades internament pel microcontrolador, mentre que les interrupcions externes són generades per addicionals dispositius d'interfície o commutadors que estan connectats externament al microcontrolador. Aquestes interrupcions externes es poden activar a la vora o activar el nivell. Quan es produeix una interrupció, el microcontrolador executa la rutina del servei d’interrupcions de manera que la ubicació de la memòria correspongui a la interrupció que l’habiliti. La interrupció corresponent a la ubicació de la memòria es dóna a la taula de vectors d'interrupció següent.

Taula de vector d'interrupció

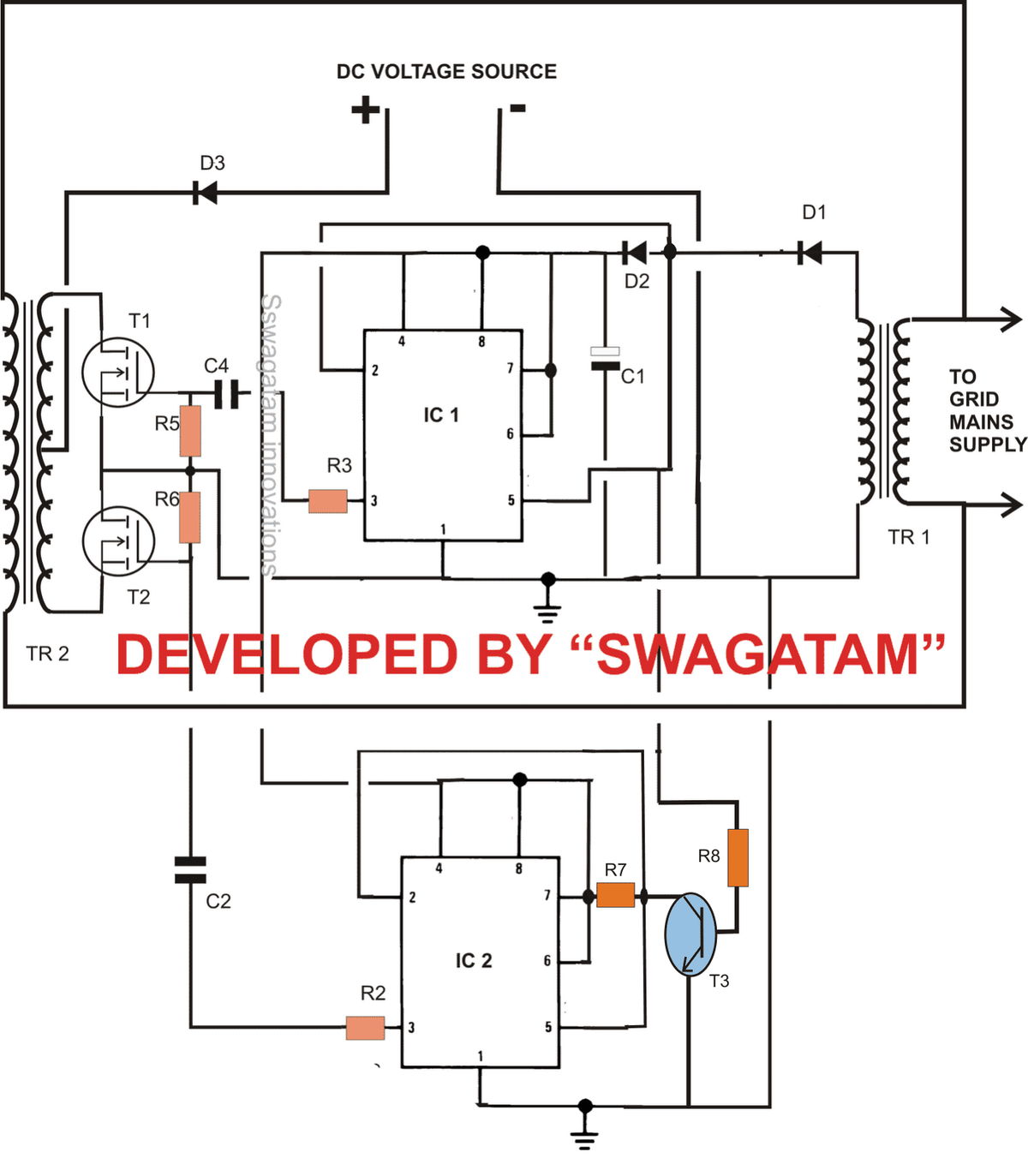

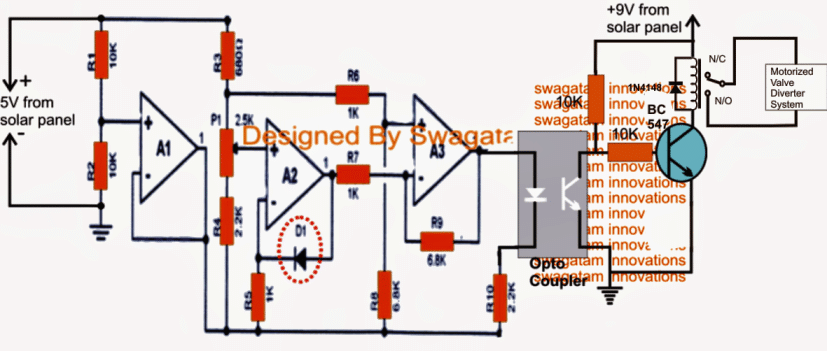

Estructura d’interrupció del microcontrolador 8051

Després de 'RESET', totes les interrupcions es desactiven i, per tant, totes aquestes interrupcions han de ser habilitades per un programari. En totes aquestes cinc interrupcions, si hi ha algú o totes activades, estableix els indicadors d'interrupció corresponents tal com es mostra a la figura. Totes aquestes interrupcions es poden definir o esborrar per bit en algun registre de funcions especials que està habilitat per interrupció (IE), i això al seu torn depèn de la prioritat, que s’executa mitjançant el registre de prioritats d’interrupció IP.

Estructura d'interrupció del microcontrolador 8051

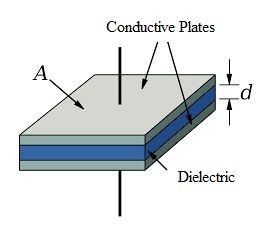

Registre d'Interrupt Enable (IE): Aquest registre s’encarrega d’habilitar i desactivar la interrupció. És un registre una mica adreçable en el qual s’ha d’establir EA en un per habilitar les interrupcions. El bit corresponent d’aquest registre permet interrupcions particulars com temporitzador, entrades externes i sèries. Al registre IE següent, el bit corresponent a 1 activa la interrupció i 0 desactiva la interrupció.

Registre d'Interrupt Enable (IE)

Registre de prioritat d'interrupció (IP): També és possible canviar els nivells de prioritat de les interrupcions configurant o esborrant el bit corresponent al registre de prioritat d'interrupció (IP) tal com es mostra a la figura. Això permet que la interrupció de baixa prioritat interrompi la interrupció de màxima prioritat, però prohibeix la interrupció per una altra interrupció de baixa prioritat. De la mateixa manera, la interrupció d'alta prioritat no es pot interrompre. Si aquestes prioritats d'interrupció no estan programades, el microcontrolador s'executa de manera predefinida i el seu ordre és INT0, TF0, INT1, TF1 i SI.

Registre IP

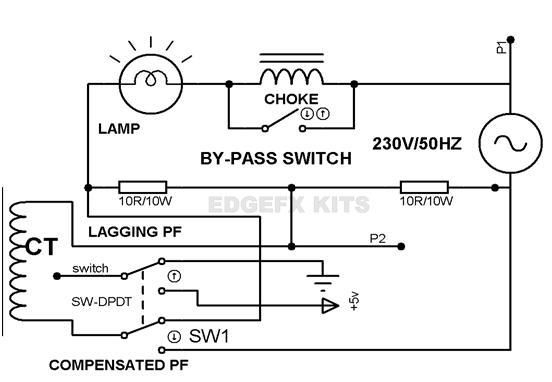

Registre TCON: A més dels dos registres anteriors, el registre TCON especifica el tipus d’interrupció externa al microcontrolador 8051, tal com es mostra a la figura. Les dues interrupcions externes, ja siguin activades a la vora o al nivell, s'especifiquen per aquest registre mitjançant un conjunt o esborren els bits adequats. I, a més, és un registre una mica adreçable.

Registre TCON

Programació d’interrupcions el 8051

1. Programació d'interrupcions temporitzades

Les interrupcions del temporitzador 0 i del temporitzador 1 són generades pels bits de registre de temporitzador TF0 i TF1. Aquestes interrupcions programació mitjançant codi C. implica:

- Selecció del temporitzador mitjançant la configuració del registre TMOD i el seu mode de funcionament.

- Triar i carregar els valors inicials de TLx i THx per als modes adequats.

- Habilitació dels registres IE i del bit de temporitzador corresponent.

- Configuració del bit d'execució del temporitzador per iniciar el temporitzador.

- Escrivint la subrutina per al temporitzador pel temps necessari i esborreu el valor del temporitzador TRx al final de la subrutina.

Programació d’interrupció del temporitzador

2. Programació externa d’interrupció de maquinari

Els microcontroladors 8051 consten de dues interrupcions de maquinari extern: INT0 i INT1, tal com es va comentar anteriorment. Estan habilitats al pin 3.2 i al pin 3.3. Aquests es poden activar a la vora o activar el nivell. En el desencadenament de nivell, el mínim al pin 3.2 habilita la interrupció, mentre que al pin 3.2: la transició entre alt i baix permet la interrupció activada per la vora. Aquest activador de vora o activació de nivell el decideix el registre TCON que s’ha comentat anteriorment. El procediment de programació el 8051 és el següent:

- Activeu el bit d'interrupció extern corresponent al registre IE.

- Si es desencadena de nivell, només cal que escriviu la subrutina adequada a aquesta interrupció o bé activeu el bit de registre TCON corresponent a la interrupció activada per la vora, ja sigui INT0 o INT1.

Programació d’interrupcions de maquinari extern

3. Programació d’interrupcions de comunicació en sèrie

Les interrupcions de comunicació sèrie apareixen quan es necessita enviar o rebre dades. Com que s'estableix un bit d'interrupció per als indicadors TI (Transfer Interrupt) i RI (Receiver Interrupt), la rutina del servei d'interrupció ha d'examinar aquests indicadors per conèixer la interrupció real.

El funcionament OR lògic d'aquests dos indicadors (RI i TI) provoca aquesta interrupció i només el programari neteja. Aquí s’utilitza un registre especial SCON per controlar comunicació operació habilitant els bits corresponents.

- Configureu el registre IE per habilitar la interrupció sèrie

- Configureu el registre SCON per rebre o transferir operacions

- Escriviu una subrutina per a aquesta interrupció amb la funció adequada i esborreu els indicadors TI o RI amb aquesta rutina.

Programació d’interrupcions en sèrie

Es tracta d’interrupcions en el microcontrolador 8051, els tipus, la seva estructura i la seva programació. Espero que hagueu rebut bona informació d’aquest article. A més, ens podeu escriure a la secció de comentaris següent per a la implementació en temps real de projectes de microcontroladors perquè puguem ajudar-lo per obtenir una millor experiència pràctica.

Crèdits fotogràfics

- Interromp en el microcontrolador 8051 per enginyersgarage

- Taula vector d'interrupció per 8051projects

- Estructura d'interrupció del microcontrolador 8051 per pinzell

- Registre Interrupt Enable (IE) abans electroons

- Registre IP per avui en dia

- Registre TCON per avui en dia