El Pantalla de set segments s’utilitza amb més freqüència la pantalla digital en calculadores, comptadors digitals, rellotges digitals, instruments de mesura, etc. Normalment, les pantalles com LEDs i LCD s’utilitzen per mostrar els caràcters i els números numèrics. Però, es fa servir una pantalla de set segments per mostrar tant els números com els caràcters. Aquestes pantalles són freqüentment impulsades per les fases de sortida del digital circuits integrats com els comptadors de dècades i els pestells. No obstant això, les sortides d'aquests són de tipus de 4 bits BCD (decimal codificat binari) , per tant, no és adequat per operar directament la pantalla de set segments. Per a això, es pot utilitzar un descodificador de pantalla per convertir el codi BCD a un codi de set segments. En general, té quatre línies d’entrada i set línies de sortida. En aquest article es parla de com dissenyar una pantalla BCD a set segments circuit de descodificació utilitzant portes lògiques.

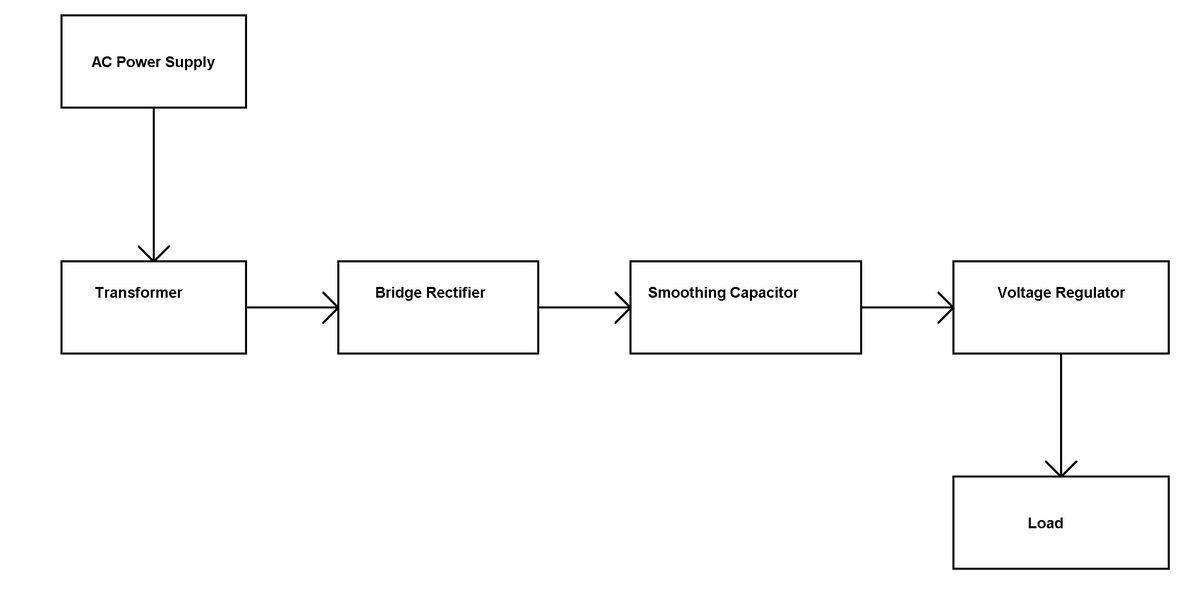

Teoria del descodificador de visualització de BCD a set segments

El descodificador és un component essencial a Descodificador de BCD a set segments . Un descodificador no és res més que un circuit lògic combinacional que s’utilitza principalment per convertir un BCD en un nombre decimal equivalent. Pot ser un descodificador de BCD a set segments. A circuit lògic combinacional es pot construir amb portes lògiques que inclouen entrades i sortides. La sortida d’aquest circuit es troba principalment en l’estat actual de les entrades. Els millors exemples d’aquest circuit són multiplexors , desmultiplexors , sumadors, restants , codificadors, descodificadors, etc.

Visualització de BCD a set segments

El disseny del circuit, així com el funcionament, depenen principalment dels conceptes de Àlgebra de Boole així com les portes lògiques. Un segment de set Circuit de visualització LED es pot construir amb vuit LEDs. Els terminals comuns són un ànode o càtode. Una pantalla general de set segments de càtode inclou 8 pins on els 7 pins són pins d'entrada marcats amb de a a g i el 8è pin és un pin de terra.

Disseny del circuit de descodificació de visualització BCD a 7 segments

El disseny de Descodificador de visualització BCD a set segments el circuit consisteix principalment en quatre passos: l'anàlisi, el disseny de taules de veritat, Mapa K i dissenyar un circuit lògic combinacional mitjançant portes lògiques.

El primer pas d’aquest disseny de circuits és una anàlisi de la visualització comuna de set segments de càtode. Aquesta pantalla es pot construir amb set LEDs en forma de H. Una taula de veritat d’aquest circuit es pot dissenyar mitjançant les combinacions d’entrades per a cada dígit decimal. Per exemple, el número decimal '1' controlaria una barreja de b & c.

El segon pas és el disseny de taules de veritat mitjançant la llista la pantalla senyals d'entrada-7, nombres binaris equivalents de quatre dígits i número decimal.

El disseny de la taula de veritat per al descodificador depèn principalment del tipus de pantalla. Ja hem comentat anteriorment que, per a una visualització de càtode comú, la sortida del descodificador ha de ser alta per parpellejar el segment.

A continuació es mostra la forma tabular d’un descodificador de BCD a 7 segments amb una pantalla de càtode comuna. La taula de veritat consta de set columnes o / p equivalents a cadascun dels set segments. Per exemple, la columna per a un segment il·lustra els diversos arranjaments per als quals s’ha d’il·luminar. Per tant, el segment ‘a’- és enèrgic per als dígits com 0, 2, 3, 5, 6, 7, 8 i 9.

Dígit | X | I | AMB | IN | a | b | c | d | és | f | g |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 2 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

3 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 4 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

5 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 6 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

7 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

En utilitzar la taula de veritat anterior, per a cada funció de sortida, es pot escriure l’expressió booleana.

a = F1 (X, Y, Z, W) = ∑m (0, 2, 3, 5, 7, 8, 9)

b = F2 (X, Y, Z, W) = ∑m (0, 1, 2, 3, 4, 7, 8, 9)

c = F3 (X, Y, Z, W) = ∑m (0, 1, 3, 4, 5, 6, 7, 8, 9)

d = F4 (X, Y, Z, W) = ∑m (0, 2, 3, 5, 6, 8)

e = F5 (X, Y, Z, W) = ∑m (0, 2, 6, 8)

f = F6 (X, Y, Z, W) = ∑m (0, 4, 5, 6, 8, 9)

g = F7 (X, Y, Z, W) = ∑m (2, 3, 4, 5, 6, 8, 9)

El tercer pas en aquest disseny consisteix principalment en el disseny de Mapa K (mapa de Karnaugh) per a cada expressió de sortida i després escurçar-les per obtenir una combinació lògica d'entrades per a cada sortida.

Simplificació de Karnaugh -Map

La simplificació del mapa k del descodificador de segment de càtode comú de 7 es pot fer per planificar el circuit combinacional. A partir de la simplificació del mapa K anterior, podem obtenir equacions de sortida com aquestes

a = X + Z + YW + Y'W '

b = Y ’+ Z’W’ + ZW

c = Y + Z '+ W

d = Y’W ’+ ZW’ + YZ’W + Y’Z + X

e = Y'W '+ ZW'

f = X + Z’W ’+ YZ’ + YW ’

g = X + YZ '+ Y'Z + ZW'

L'últim pas és dissenyar un circuit lògic mitjançant les equacions del mapa k anterior. Es pot construir un circuit combinacional mitjançant 4 entrades, concretament A, B, C, D i sortides a la pantalla com a, b, c, d, e, f, g. El funcionament del circuit lògic anterior només es pot entendre amb l'ajuda de la taula de veritat. Un cop tots els i / ps estiguin connectats a una lògica petita.

Circuit de descodificació de BCD a set segments

A continuació, la sortida del circuit lògic combinacional conduirà tots i cadascun dels LED de sortida a part de ‘g’ fins a la transmissió. Per tant, s’exposarà el número ‘0’. De la mateixa manera, per a qualsevol altra agrupació dels commutadors d'entrada, es produiria el mateix procés.

Visualització de set segments BCD mitjançant IC 7447

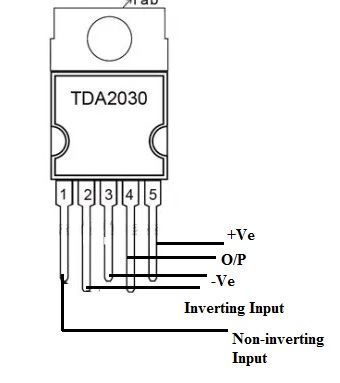

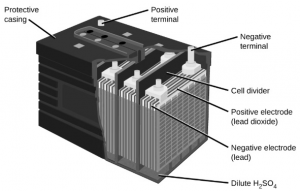

Bàsicament, els díodes emissors de llum són de dos tipus: el càtode comú CC, així com l’ànode comú CA. Al càtode comú, tots els vuit terminals d'ànode utilitzen només un terminal de càtode únic, que és familiar. Mentre que en ànode comú, el terminal familiar per a tot el terminal de càtode és de tipus ànode.

Pantalla de set segments BCD mitjançant IC7447

Un descodificador és un tipus de circuit lògic combinacional que connecta les dades binàries de línies d'entrada n a línies de sortida 2n. El IC7447 IC és un descodificador de BCD a set segments. Aquest IC7447 obté el decimal codificat binari com l'entrada, així com dóna les sortides com el codi de set segments relacionat.

Per tant, es tracta de la visualització del descodificador de BCD a 7 segments. A partir de la informació anterior, finalment, podem concloure que aquest circuit es pot canviar amb temporitzadors, així com comptadors per mostrar els impulsos CLK, i també es pot utilitzar com a circuit de temporitzador. Aquí teniu una pregunta, què és Karnaugh -Map?