L'IC 4040 és tècnicament un xip de comptador de ondulació binari de 12 etapes, en paraules simples, un dispositiu que produirà una sortida de freqüència retardada calculada en resposta a cada pols aplicat a la seva entrada de rellotge. Aquest retard s'incrementa a la velocitat de 2 ^ (n) on n és l'ordre de fixació en la seqüència de les seves sortides.

Especificacions tècniques principals

Les principals característiques i especificacions del CI es poden entendre de la següent manera:

Completament emmagatzemades 12 sortides que divideixen els rellotges d’entrada a la velocitat 2 ^ (n) on n = l’ordre de pinout que comença des de Q0 fins a Q11.

La seqüenciació anterior de les sortides es produeix en resposta a cada vora descendent del rellotge aplicat al pinout CP de l'entrada del rellotge. La CI respondrà de manera tan efectiva fins i tot a un impuls de rellotge que cau relativament lent.

Una única entrada de reinici mestre asíncron (MR) que restableix totes les sortides a zero quan s'aplica una lògica alta, mentre que una lògica baixa constant permet que l'IC es mantingui actiu.

El CI es fa totalment operatiu amb Vdd a partir de 3V i manté una característica operativa constant fins i tot a tensions al voltant de 15V.

Examinem els paràmetres que no s’han de superar per a l’IC 4040

- Voltatge de subministrament (Vdd) = Normalment entre 3V i 15V, sent el límit màxim 18V.

- Voltatge d'entrada (Vi) = El voltatge que es pot aplicar a les entrades com CP, MR, etc. ha de ser normalment inferior a Vdd o com a màxim = Vdd + 0,5V

- Requisit de corrent òptim de funcionament = 50 mA ja que hi ha tantes sortides implicades i cada sortida

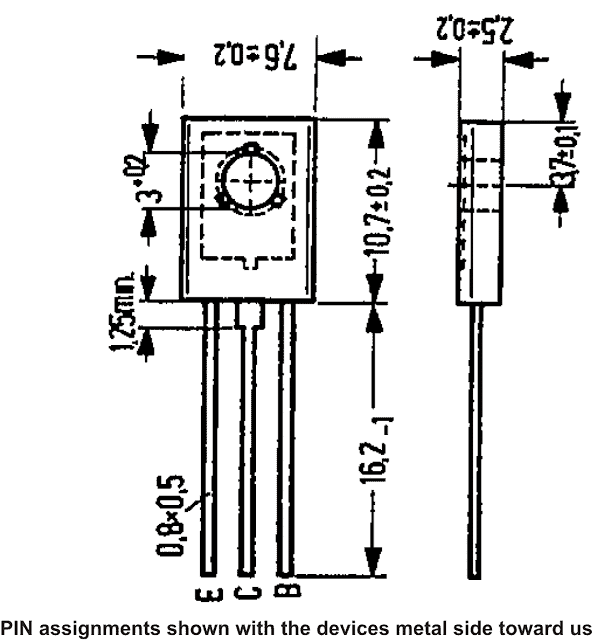

Detalls del pinout

El diagrama anterior mostra la configuració de pinout de l'IC 4040, que es pot avaluar tal com es mostra a sota:

Els pinouts Q0 a Q11 són les sortides del CI.

- Vss és el pin de terra.

- Vdd és el pin positiu.

- MR és el pinout de restabliment

- CP és l'entrada de rellotge.

Seqüència de temps

Analitzem ara la seqüència de temps de sortida de l'IC 4040. Com es mostra al següent diagrama, podem veure i comprendre els detalls següents:

Mentre l’entrada MR sigui alta, les sortides IC no produeixen cap resposta. Tan aviat com baixa, l'IC comença a respondre i compta el rellotge d'entrada a l'entrada CP.

El primer pin de sortida Q0 augmenta després del rellotge 2 ^ (n) a CP, és a dir, = 2 ^ (0) = 1, és a dir, Q0 augmenta a la vora descendent del primer pols i baixa en resposta a la vora descendent de la rellotge posterior, etc.

De manera similar, Q1 augmenta després de 2 ^ (1) = 2, és a dir, augmenta tan aviat com es detecta una vora descendent del segon rellotge i baixa a la vora descendent del quart rellotge posterior, etc.

De manera idèntica, Q2 va alts i baixos després de 2 ^ (2) = vores caigudes del quart rellotge, etc.

La seqüència anterior es continua fins a Q11, en resposta a les entrades de rellotge sostingudes a CP.

Significa que si suposem que el CP té un impuls de 1Hz, Q11 augmentaria després de 2 ^ 11 segons o després de 2048 segons que és igual a 34 minuts aproximadament, només imagineu el rang de retard que podeu aconseguir simplement augmentant l’entrada de rellotge segons o potser per minuts.

Consells d'aplicació

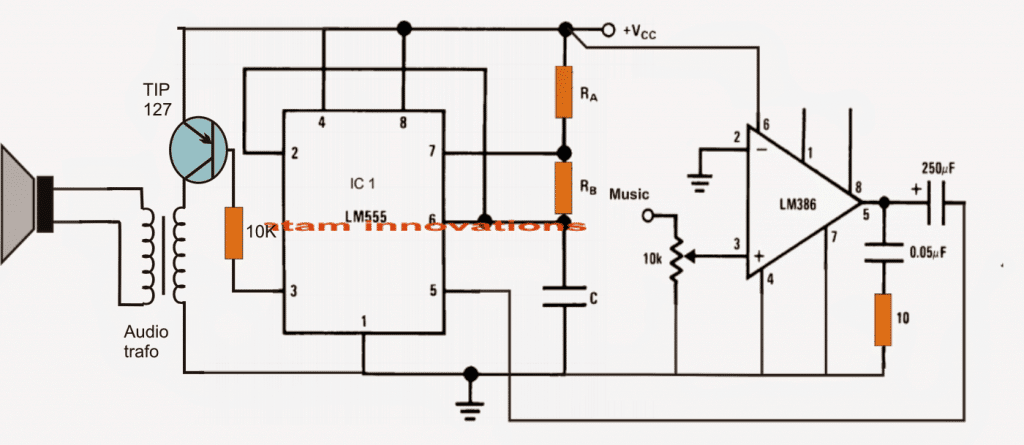

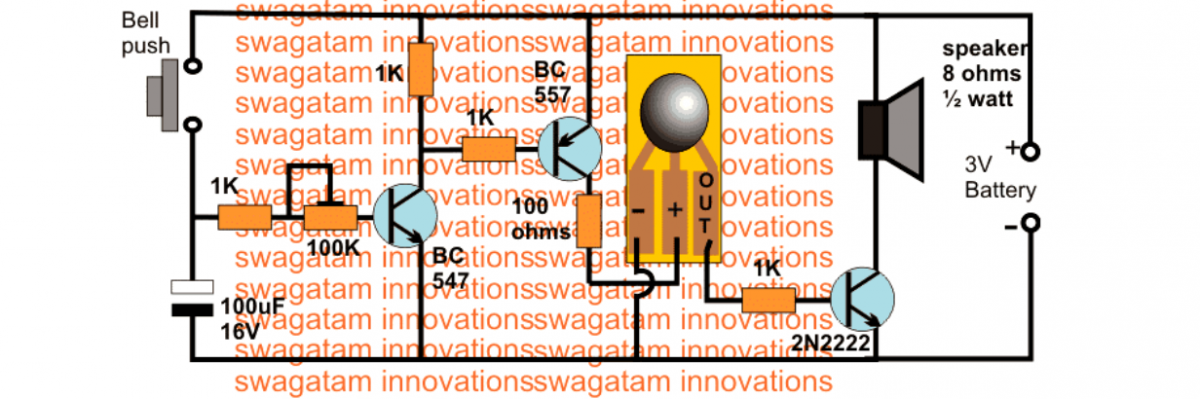

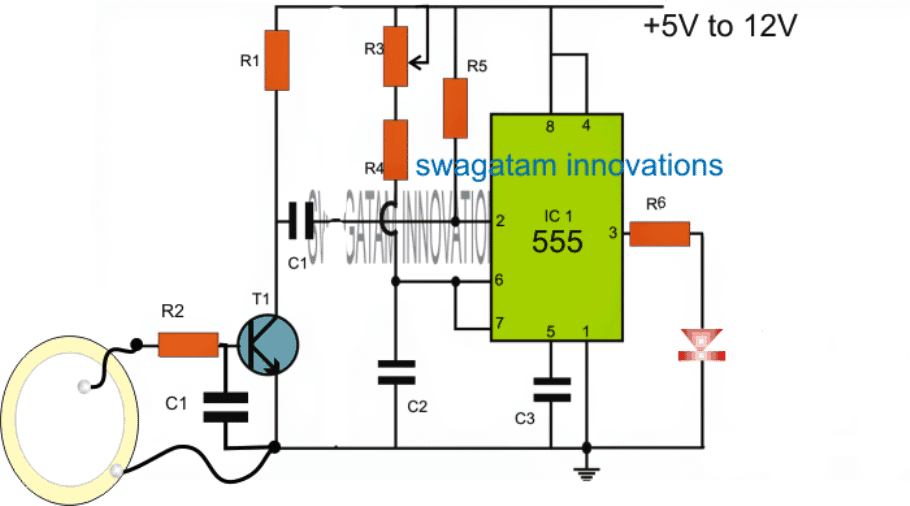

A partir de l’anàlisi detallada anterior del full de dades IC 4040 podem concloure que l’IC és normalment adequat per a totes les aplicacions que impliquin requisits de divisió de freqüències o requisits de generació de períodes de temps retardats.

Per tant, podria ser especialment adequat per a aplicacions de circuits divisors de freqüència, temporitzadors de llarga durada, intermitents i altres aplicacions similars.

Anterior: fer servir dissipador d’alumini amb tires d’alumini per a LEDs d’alta potència en lloc de PCB Següent: Circuit de temporitzador d’agitador de motor de rentadora